Public Version

# OMAP4430 Multimedia Device Silicon Errata Silicon Revision 2.3, 2.2, 2.1, 2.0

Texas Instruments OMAP™ Family of Products Version Q

# **Errata**

Literature Number: SWPZ009Q

October 2010–Revised September 2013

### **WARNING: EXPORT NOTICE**

Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from Disclosing party under this Agreement, or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorisation from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws. This provision shall survive termination or expiration of this Agreement.

According to our best knowledge of the state and end-use of this product or technology, and in compliance with the export control regulations of dual-use goods in force in the origin and exporting countries, this technology is classified as follows:

US ECCN: 3E991 EU ECCN: EAR99

And may require export or re-export license for shipping it in compliance

with the applicable regulations of certain countries.

#### Public Version

## **Contents**

| Prefa | ace  |                                                                                                        | 8  |

|-------|------|--------------------------------------------------------------------------------------------------------|----|

| 1     | Bugs |                                                                                                        | 19 |

|       | 1.1  | Delay needed to read some GP timer, WD timer and sync timer registers after wakeup                     | 20 |

|       | 1.2  | MDR1 access can freeze UART module                                                                     |    |

|       | 1.3  | DSI: Minimum Of 2 Pixels Should Be Transferred Through DISPC Video Port                                | 22 |

|       | 1.4  | DSI: Cancel Tearing Effect Transfer                                                                    | 23 |

|       | 1.5  | DSI: RX FIFO Fullness                                                                                  | 24 |

|       | 1.6  | DSI: Access Restriction On DSI_TIMING2 Register                                                        | 25 |

|       | 1.7  | DSI: Tx FIFO Flush Is Not Supported                                                                    | 26 |

|       | 1.8  | sDMA Channel Is Not Disabled After A Transaction Error                                                 | 27 |

|       | 1.9  | DSI SOF Packet Not Send                                                                                | 28 |

|       | 1.10 | SIMCOP Lens Distortion Correction issue                                                                | 29 |

|       | 1.11 | ISS: SOFTRESET Bit Status Not Working For Circular Buffer                                              | 30 |

|       | 1.12 | ISS: SOFTRESET Bit Status Not Working For Burst Translation Engine                                     | 31 |

|       | 1.13 | ISS State Can Be Corrupted During Debug Mode                                                           | 32 |

|       | 1.14 | DSI VSYNC HSYNC Detection In Video Mode                                                                | 33 |

|       | 1.15 | Dual Video Mode                                                                                        | 34 |

|       | 1.16 | Deadlock Between DISPC And DSI When PCD = 2, VP_CLK_RATIO = 0                                          | 35 |

|       | 1.17 | I2C: In SCCB Mode, Under Specific Conditions, The Module Might Hold The Bus By Keeping SCL Low.        | 36 |

|       | 1.18 | I2C: Wrong Behavior When A Data With MSB 0 Is Put In The FIFO Before A Transfer With SBLOCK Is Started | 37 |

|       | 1.19 | I2C: After An Arbitration Is Lost, The Module Starts Incorrectly The Next Transfer Incorrectly         | 38 |

|       | 1.20 | Deep Power-Down Support During Off Mode                                                                | 39 |

|       | 1.21 | RTA Feature Is Not Supported                                                                           | 40 |

|       | 1.22 | I/O Daisy Wakeup During Device Off Mode Transition Stalls the Device Power Transition                  |    |

|       | 1.23 | Off Mode Power Consumption On VDD_WKUP                                                                 | 42 |

|       | 1.24 | Wkup Clk Recycling Needed After Warm Reset                                                             | 43 |

|       | 1.25 | DMM Hang Issue During Unmapped Accesses                                                                | 44 |

|       | 1.26 | HS USB Host HSIC Not Functional                                                                        | 45 |

|       | 1.27 | I2C SCL and SDA Glitch At Reset Release                                                                | 46 |

|       | 1.28 | Retention/Sleep Voltage Transitions Ramp Time                                                          | 48 |

|       | 1.29 | Interrupt Enable Registers Not Restored                                                                | 49 |

|       | 1.30 | MMCHS_HCTL.HSPE Is Not Functional                                                                      | 50 |

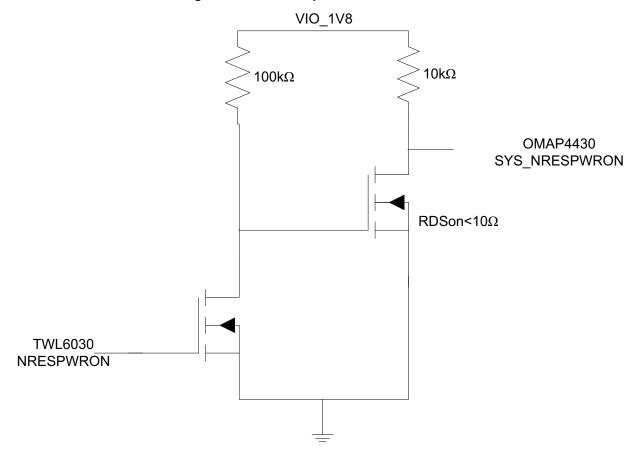

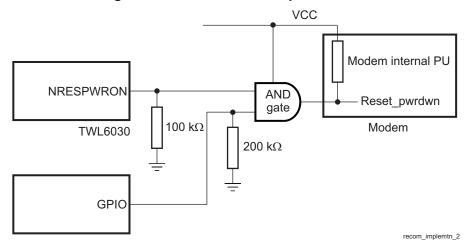

|       | 1.31 | NRESPWRON Pin Issue While Supplies are Ramping                                                         | 51 |

|       | 1.32 | I/O Glitch At Reset Release                                                                            |    |

|       | 1.33 | SDRAM Access During Heavy MPU Accesses                                                                 | 55 |

|       | 1.34 | Wrong Access In 1D Burst For YUV4:2:0-NV12 Format                                                      | 56 |

|       | 1.35 | LPDDR2 Corruption After OFF Mode Transition When CS1 Is Used On EMIF                                   | 57 |

|       | 1.36 | Time-out Interrupt May Never Come When Device Is Not Detected (1-Wire Mode)                            | 58 |

|       | 1.37 | Usbb*_hsic Pads Pullup/Down Control Not Working As Expected                                            | 59 |

|       | 1.38 | USB HOST EHCI In TLL Mode Will See The Port Being Disabled Upon Resume Or Remote Wakeup                |    |

|       | 1.39 | Status of DSI LDO Is Not Reported to DSI Protocol Engine                                               |    |

|       | 1.40 | HSI Break Frame Corrupt OnGoing Transfer                                                               | 63 |

| 1.41 | HSI Error Counters Cannot Be Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.42 | McPDM/DMIC Issue With Software Reset With SW_xx_RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 1.43 | CM1 And CM2 OCP Interface Hangs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 1.44 | UART: Extra Assertion of UARTi_DMA_TX Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 1.45 | USB OTG Software Initiated ULPI Accesses To PHY Registers Can Halt the Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1.46 | ISS-SIMCOP: ISS-LSC Not Transparent After Prefetch Error Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 1.47 | Phoenix Registers Value Are Lost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 1.48 | MMC1 Is Wrongly Marked As Permanent Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1.49 | Bit 7 from Tracing Vector 1 Is Wrongly Set For XIP Memory Booting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 1.50 | Incorrect Pad Muxing in MMC2 Boot Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 1.51 | UART: In an RX Wake-up Mechanism, the First Received Character Can be Lost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1.52 | Platform Hangs When CPU Tries To Configure The EMIF Firewall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 1.53 | Observability on sdma_req64 and 65 Does Not Have Expected Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 1.54 | DDR PHY Must be Reset After Leaving OSWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 1.55 | USB TLL Hold Timing Violation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 1.56 | Async Bridge Corruption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 1.57 | Keyboard Key Up Event Can Be Missed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 1.58 | USB HOST - Impossible To Attach a FS Device To An EHCI Port. Handoff To OHCI Is Not Functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 1.59 | USB HOST EHCI - Port Resume Fails On Second Resume Iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 1.60 | System I2C hang due to miss of Bus Clear support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 1.61 | HSI: Issues In Suspending and Resuming Communication (HSR and HST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 1.62 | HSI: Issue with SW reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 1.63 | DMA4 generates unexpected transaction on WR port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 1.64 | DMA4 channel fails to continue with descriptor load when Pause bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 88 |

| 1.65 | HSI: DSP Swakeup generated is the same than MPU Swakeup. System can't enter in off mode due to the DSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90   |

| 1.66 | CBUFF Ready Window Event in Write Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 1.67 | CSI-2 Receiver Executes Software Reset Unconditionally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 1.68 | USB Host TLL Bit-stuffing Feature Is Broken                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 1.69 | ISP H3A Hangs Due to Unstable Vertical Sync Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 1.70 | GPIO IRQ Not Generated After MPU Idle if IRQSTATUS Bits Not Cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 1.71 | DSI PLL Signal is Not available on Hardware Observability Pads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 1.72 | Blending Calculation Error When Premultiply Alpha is Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 1.72 | HS USB: Multiple OFF Mode Transitions Introduce Corruption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 1.74 | Presence Rate Generation Not Supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |